Cell BE - A Network on a Chip

From Computing and Software Wiki

Network on a chip (NOC) is a paradigm in the design of parallel hardware architecture. It differs from System on a chip (SOC) by featuring generic communication channels between processor elements instead of specialized buses to simplify chip design. Network on a chip systems have the ability to have processing elements operating on different data elements simultaneously without special framework. These characteristics allow better energy-performance characteristics[1]

. The Cell Broadband Engine (Cell BE) is a network on a chip design in production by Sony, Toshiba and IBM (STI). The Cell BE demonstrates these characteristics in a high performance, scalable production architecture.

Contents |

Cell BE Architecture

Processors

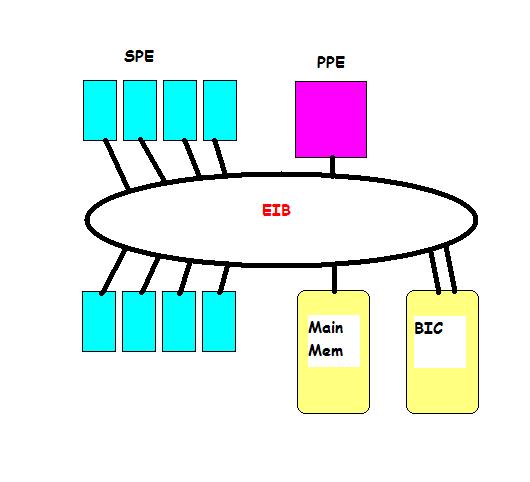

The Cell BE is comprised on 2 primary processor types; 1 Power PC Element and 8 Synergistic Processing Elements.

Power PC Element

The Power PC Element (PPE) is a 64 bit processor responsible for running operating system functions. The PPE controls thread level parallelism, and acts as a controller for the Synergistic Processing Elements (SPEs). It supports vectorized single precision floating point operations, and IBM's quad-precision (long double) floating point format.

Synergistic Processing Element

The Synergistic Processing Element (SPE) is the main computational engine for the Cell BE. The SPE is highly optimized for floating point operations. The SPEs are capable of performing a single memory instruction and a single data operation every cycle. A common configuration is 3.2 GHz (with 26,666,666 cycles/sec). The SPE cannot directly access main memory and must request data by a request to the memory controller. The SPE contains 256kB of local store memory where a copy of the data is kept. The implication of this configuration is that once sufficient data is queued, computation can begin in step with memory transfers. Although there is an initial penalty it is quickly overcome for computations on large data sets.

Controllers

Memory Interconnect Controller

Bus Interface Controller

Element Interconnect Bus

Scalability

Roadrunner

References

[1]http://en.wikipedia.org/wiki/Network_On_Chip

See Also

External Links

--Adamssw 19:36, 12 April 2009 (EDT)